-

Notifications

You must be signed in to change notification settings - Fork 108

New issue

Have a question about this project? Sign up for a free GitHub account to open an issue and contact its maintainers and the community.

By clicking “Sign up for GitHub”, you agree to our terms of service and privacy statement. We’ll occasionally send you account related emails.

Already on GitHub? Sign in to your account

Support Intel Meteor Lake #196

Conversation

For Meteor Lake CPUs, performance and efficiency cores are mixed (unlike previous CPU generations), so the approach needs to be revisited.

Since 7ad0a49, it shows that core count for Intel® Celeron® Processor J1900 and Intel Atom® Processor Z3740 was wrong. According to Intel, new values are correct: - https://www.intel.com/content/www/us/en/products/sku/78867/intel-celeron-processor-j1900-2m-cache-up-to-2-42-ghz/specifications.html?wapkw=J1900 ==> 4c/4t - https://www.intel.com/content/www/us/en/products/sku/76759/intel-atom-processor-z3740-2m-cache-up-to-1-86-ghz/specifications.html ==> 4c/4t

|

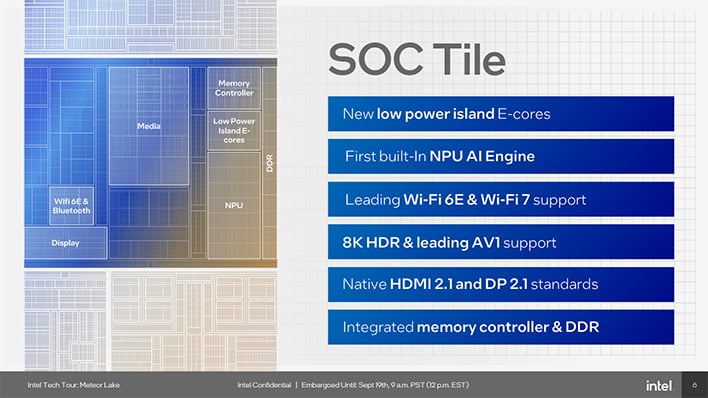

In 7ad0a49, I changed the approach in E-cores and LP E-cores are still displayed both as "efficiency". I found this thread on Intel's forum, maybe Intel will provide information about how to detect LP E-cores. |

Confirmed by Intel: https://community.intel.com/t5/Processors/Detecting-LP-E-Cores-on-Meteor-Lake-in-software/m-p/1584555/highlight/true#M70732 Added detection of LP E-Cores in 5331a4c. |

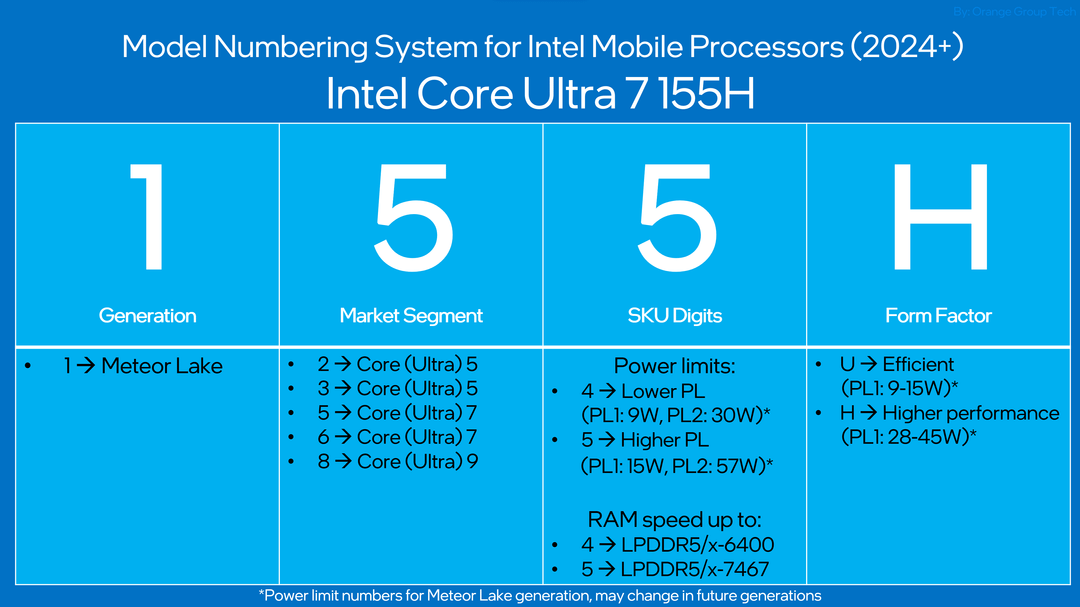

For Meteor Lake, Intel adopted a new branding: Core (Ultra) 3/5/7/9.

Also, there is a new model numbering system:

This is work in progress in 87c282b.

I found 2 CPUID dumps for Meteor Lake:

But libcpuid is not able to properly detect core types for now:

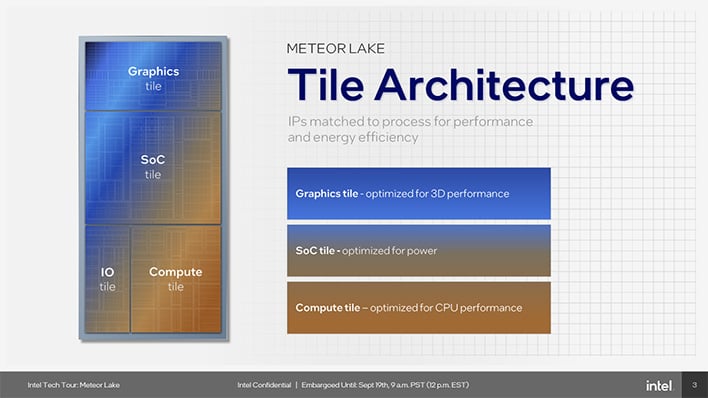

The problem is Intel is switching to tiles:

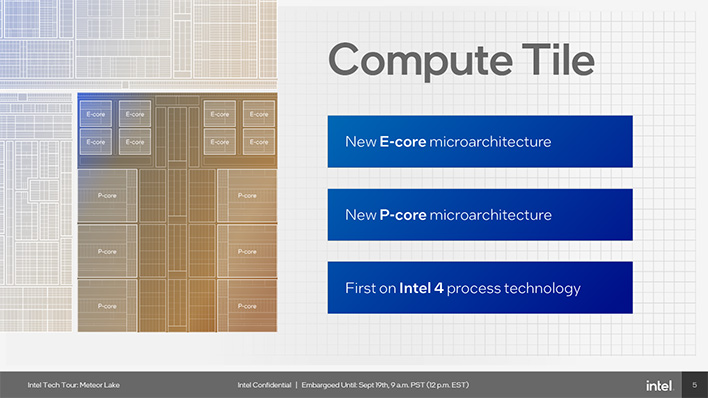

Compute tile contains both P-core (Redwood Cove) and E-cores (Crestmont):

But SoC tile also contains 2 LP-E cores (Low Power Crestmont):

And I did not find a way to differentiate Crestmont cores on Compute tile and SoC tile in Intel® 64 and IA-32 Architectures Software Developer’s Manual yet... It seems there is no L3 cache on SoC Tile while L3 cache is present for Crestmont cores on Compute Tile.